| 技術名稱 | 可擴增與模組化之AI硬體加速器 | ||

|---|---|---|---|

| 計畫單位 | 國立中興大學 | ||

| 計畫主持人 | 吳崇賓 | ||

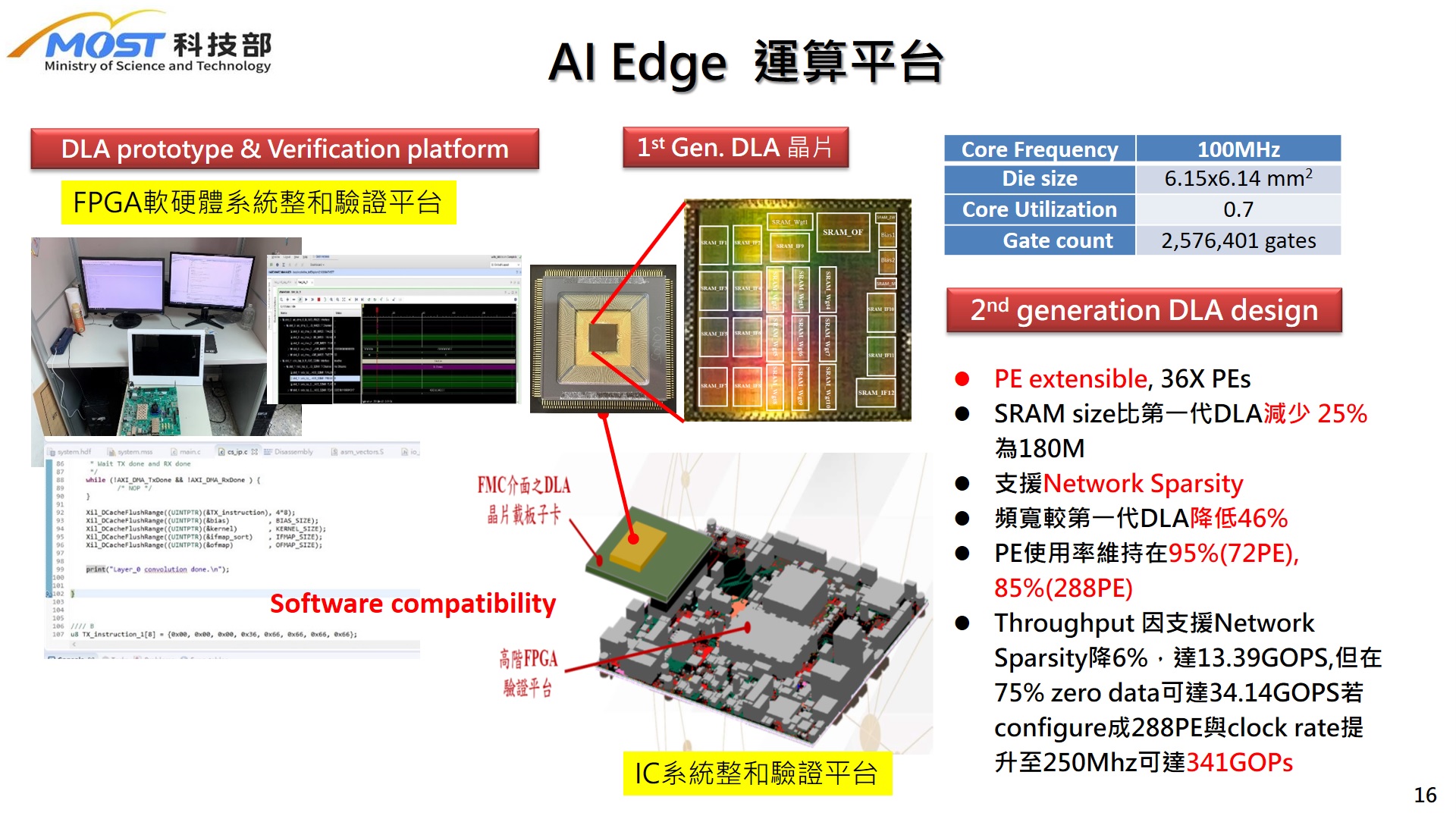

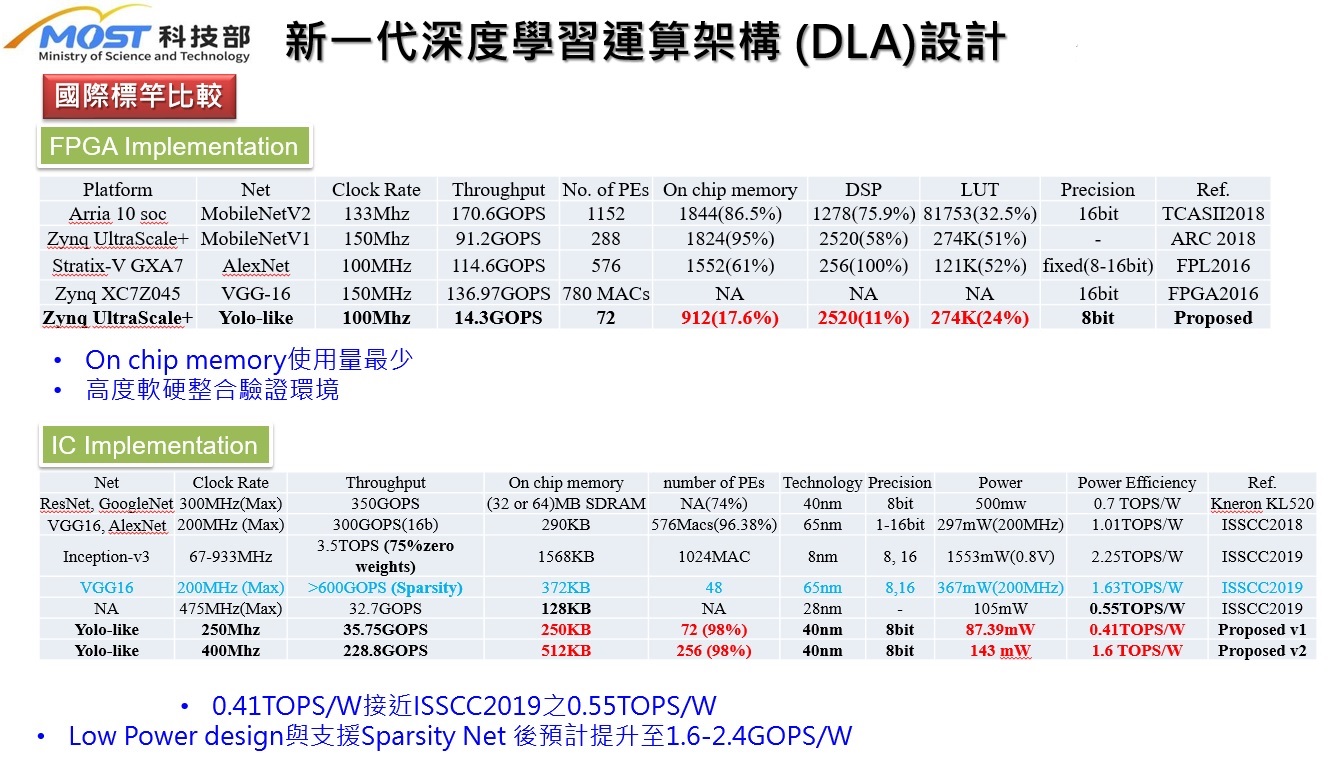

| 技術簡介 | "1. 使用PE Cluster使運算可重組,可模組化成36X的PEs,最高支援2160PEs 2. 可組態成高運算吞吐量或低功耗獨立IP,高效能下在2160PEs在200MHz可達864GOPS" |

||

| 技術影片 | |||

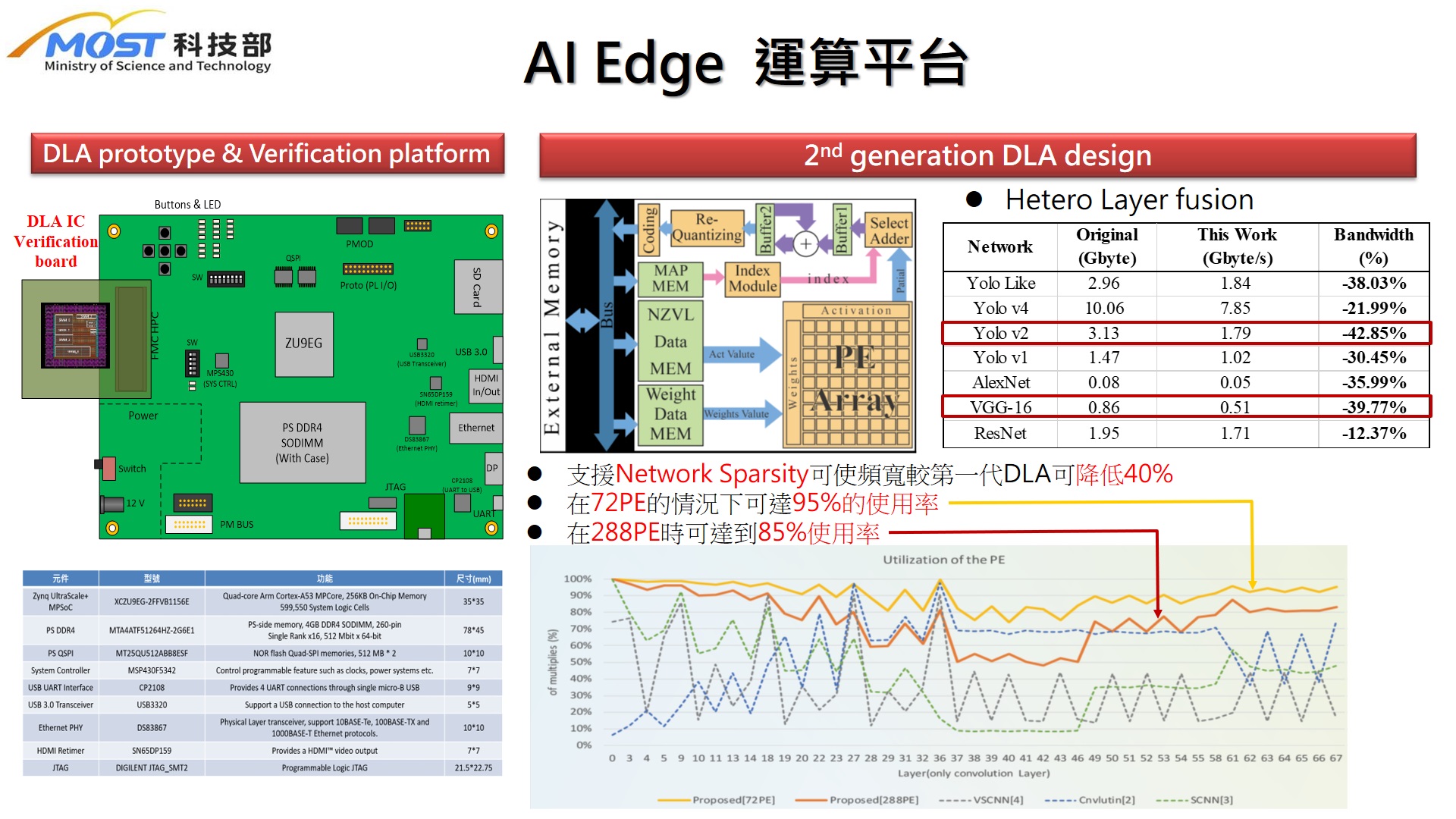

| 科學突破性 | "1. 可重組運算架構,可模組化成36X的PEs,最高支援2160PEs 2. 可組態成高運算吞吐量或低功耗獨立IP,高效能下在2160PEs在200MHz可達864GOPS,PE使用率達98 3. FPGA與IC軟硬體系統整合驗證 4. Hetero Layer Fusion可使頻寬使用效率最佳 |

||

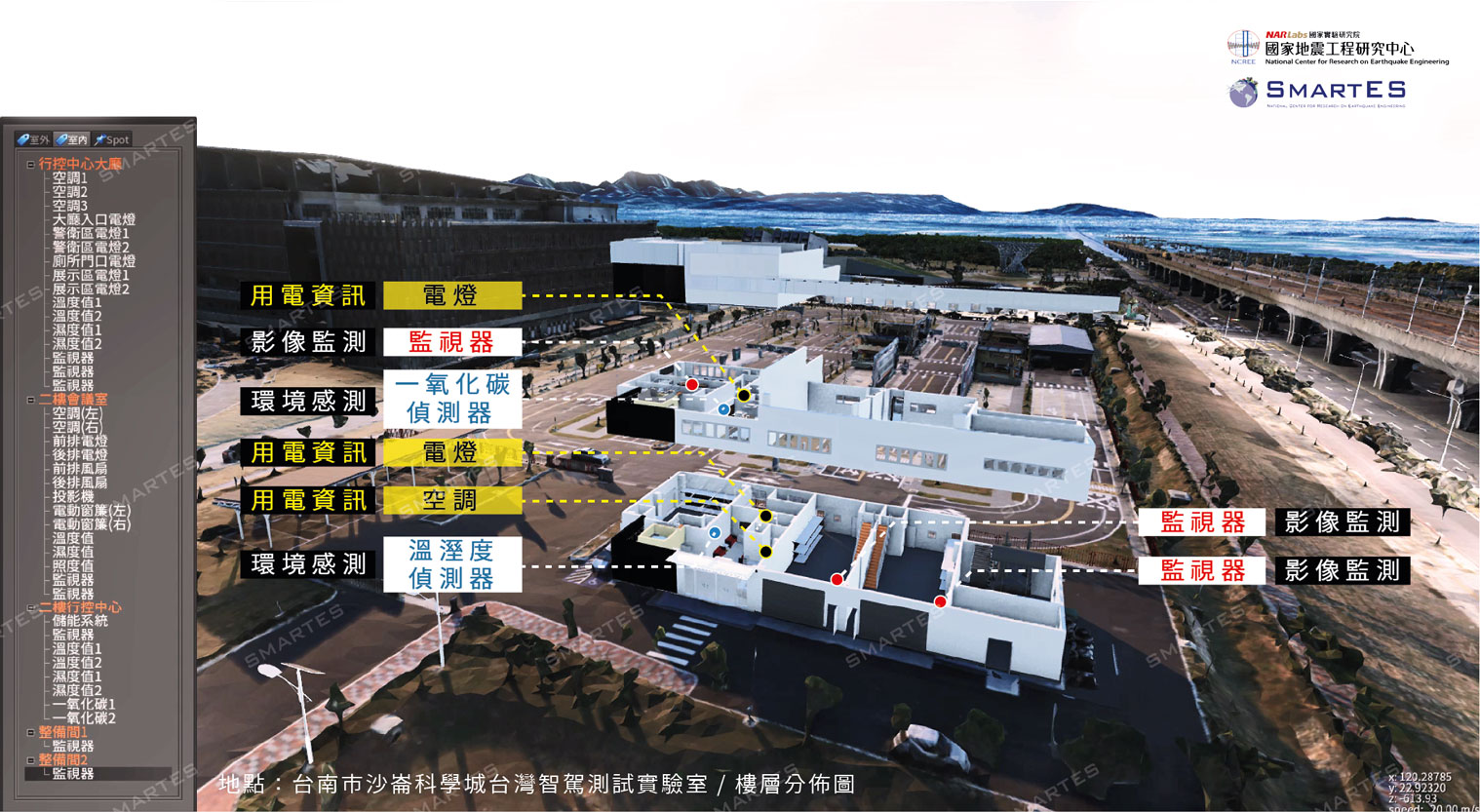

| 產業應用性 | 本技術提出彈性可擴充又可以用到限定應用的需求的IP來解決這個問題。此IP可以整合至SoC上亦可獨立開發ASIC,在驗證上可實現於FPGA整合驗證。因具有彈性擴充與模組化設計,因此根據需求快速調整,不需要大幅修改設計,縮短開發時程。 |

||

| 媒合需求 | 天使投資人、策略合作夥伴 |

||

| 關鍵字 | 深度學習 硬體架構 可重組硬體 FPGA硬體實現 AI加速器 加速運算單元 物件辨識 卷積神經網絡 模組化硬體IP 最佳化 | ||

- 聯絡人

- 詹淑琪

- 電子信箱

- shuchi@dragon.nchu.edu.tw