| 技術名稱 | 突破邏輯密度極限的單晶片三維異質元件整合與創新材料技術:實現高密度AI運算晶片的關鍵技術平台 | ||

|---|---|---|---|

| 計畫單位 | 國立陽明交通大學光電工程系 | ||

| 計畫主持人 | 劉柏村 | ||

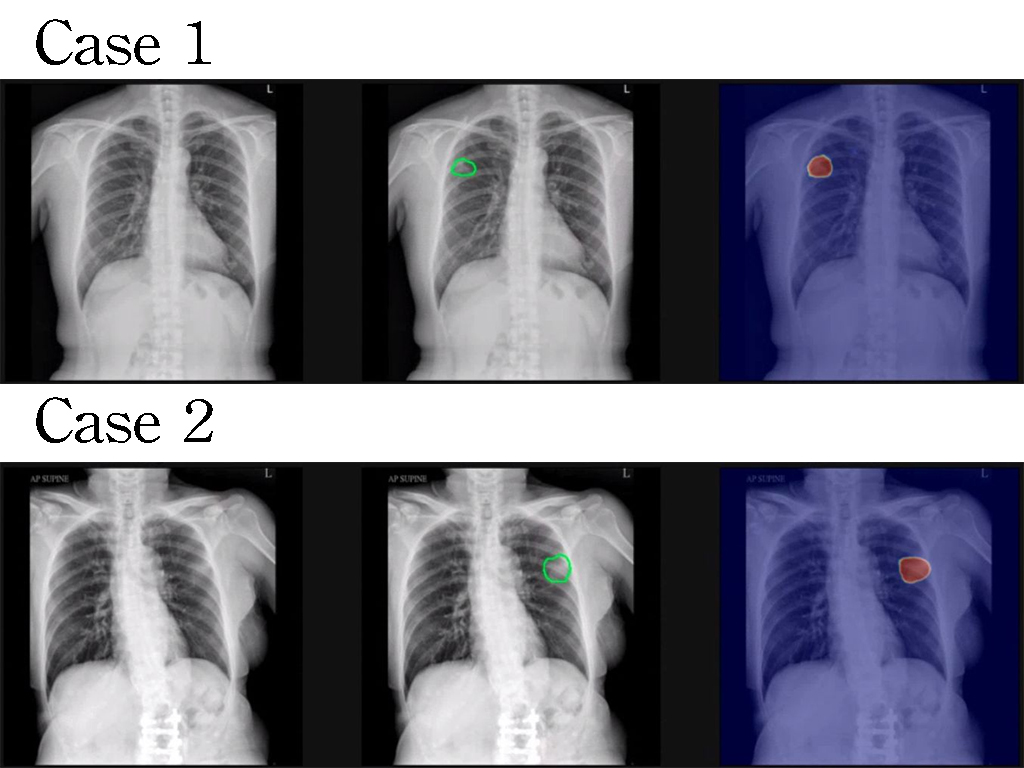

| 技術簡介 | 以100 奈米成熟製程取代16奈米以下先進製程,成功整合鍺基p-FET與氧化銦基n-FET之奈米級厚度通道,實現2M NAND/mm²技術,並朝向20M NAND/mm² (80M Trs/mm²)目標邁進。此外,首創高性能InWSnO電晶體,具極高開關比與低SS值,展現應用於AI與HPC晶片潛力。 |

||

| 科學突破性 | 本技術結合新穎材料與垂直堆疊異質元件,實現2M NAND/mm²高密度邏輯架構(等效8M Trs/mm²),並世界首創高效氧化銦鎢錫電晶體,具高速低功耗AI晶片製造技術潛力,成果發表於2025 VLSI Symposium與Advanced Science等頂尖會議與期刊。 |

||

| 產業應用性 | 以成熟製程取代先進製程,實現三維異質元件整合,達成領先全球之電晶體密集度水準(8M Trs/mm²邏輯電路),可應用於AI與高效能運算晶片製作潛力。已獲美國與台灣發明專利,具高度商品化價值。本團隊亦首創氧化銦鎢錫薄膜電晶體技術,兼具優異電性與製程相容性,為推進先進3D-IC技術之核心基礎。 |

||

| 關鍵字 | 單晶片三維整合 異質半導體整合 低熱預算製程 非晶氧化物半導體 氧化銦基奈米薄片電晶體 鍺基通道材料 三維堆疊元件架構 原子層沉積技術 反及閘邏輯電路 | ||

- 聯絡人

- 劉柏村

- 電子信箱

- ptliu@nycu.edu.tw