| Technical Name | High-Density 3D Stackable Via-RRAM | ||

|---|---|---|---|

| Project Operator | National Tsing Hua University | ||

| Project Host | 金雅琴 | ||

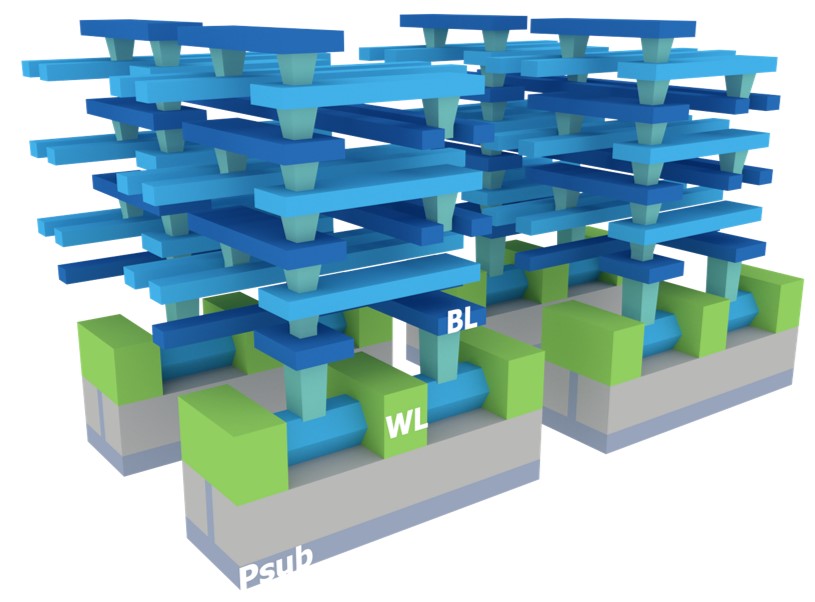

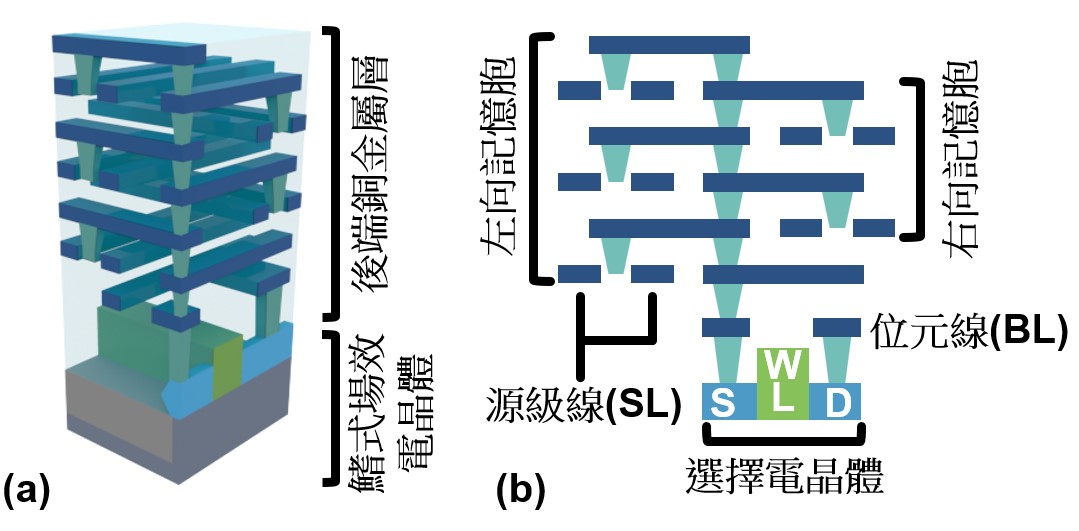

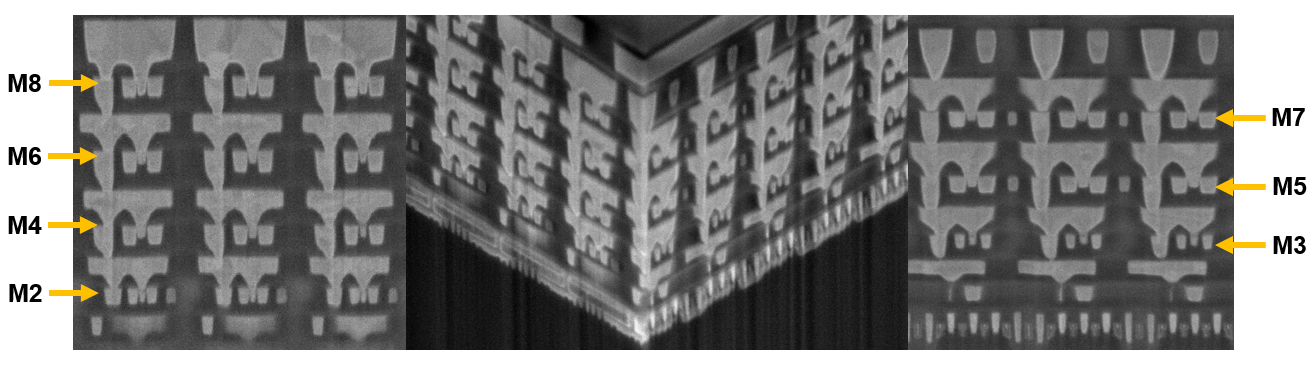

| Summary | Introducing a groundbreaking high-density 3D Via Resistive Random Access Memory (RRAM) architecture seamlessly compatible with Fin Field-Effect Transistors (FinFETs) in logic processes. Through the careful design of a structure where vias and metal wires remain intentionally isolated in the layout, a Via RRAM is ingeniously crafted. This approach offers exceptional stackability, permitting each metal wire layer within the memory unit to incorporate a pair of RRAM elements, culminating in the creation of a remarkably high-density stackable embedded memory solution. |

||

| Scientific Breakthrough | Due to its ability to be embedded within existing logic circuits, "High-Density 3D Via-RRAM" is compatible with current technology, offering increased possibilities and flexibility to meet the diverse needs of various customers. Furthermore, because this memory technology can continuously be used at technology nodes where feature sizes are continually shrinking, it can adapt to the evolution of future logic circuit processes without becoming obsolete, thus having long-term application prospects. |

||

| Industrial Applicability | "High-density 3D Via-RRAM" utilizes a leading industry-specific array configuration to significantly enhance memory storage capacity and data retrieval speed. Constructed using existing standard semiconductor FinFET backend processes, it is fully compatible and integratable with current high-speed computational chips. This technology can be sustained across advanced technology nodes, ensuring it remains competitive without being phased out due to the evolving processes of logic circuits. |

||

- Contact

- Yao-Hung Huang

- yhhuang.starlab@gapp.nthu.edu.tw

other people also saw