| 技術名稱 | 針對5G-AIOT應用廣泛興起所導致資安議題的創新硬體防護技術: 與CMOS製程平台完全相容無須多餘光罩的新式小面積低功耗高效率之「介電質熔絲崩潰單次編程記憶體」 | ||

|---|---|---|---|

| 計畫單位 | 國立中央大學 | ||

| 計畫主持人 | 謝易叡 | ||

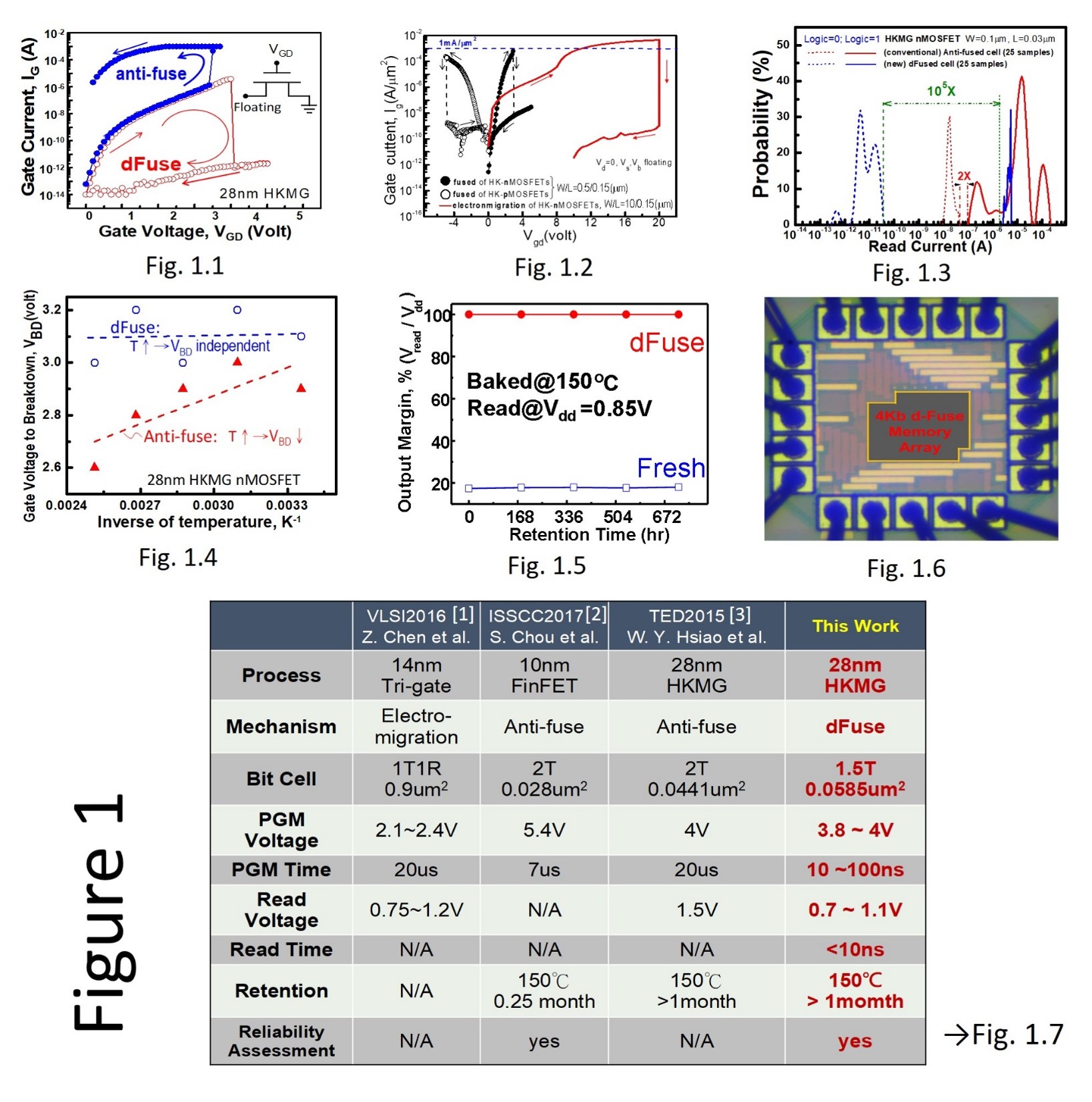

| 技術簡介 | 在SOC中,非揮發嵌入式記憶體可減少功耗、降低延遲、提升異質整合程度且大幅降低成本已成為不可或缺的角色。單次編程(OTP)嵌入式記憶體主要用來儲存開機碼和個人隱私資料既強調低成本的同時又要兼具高資料保存性與安全性。OTP主要分三類: 第一類是利用金屬連線中的金屬原子因electro-migration使導線斷線,形成熔絲型態(fused-type)。第二類是因先進製程中的電晶體閘介電層厚度不斷微縮,使得介電層的反熔絲崩潰(dielectric anti-fuse)電場大幅下降,因此利用anti-fuse機制可讓閘介電層從原本的低電導態變成高電導態,形成反熔絲型態(anti-fused type),其中又以Synopses的nMOS 閘介電層anti-fuse和eMemory的pMOS閘介電層anti-fuse主導,因anti-fuse相較於electro-migration操作上較穩定且所需面積較小,是目前OTP應用主流。第三類利用電荷儲存機制,製作浮動閘極或是nitride trap結構,形成快閃式記憶體。第一類與第二類的retention較佳而且不需額外光罩且不需利用特殊製程便可實現,成本低。第三類雖有電荷佚失問題成本也高但可以重複擦寫,具有其利基市場。本團隊首次在CMOS技術平台上發現新穎的「介電質熔絲崩潰」(dielectric fuse breakdown: dFuse)。此機制利用較高電場施加於元件閘極時,閘極介電層的Interfacial layer(IL)內的氧離子被析出,造成IL多孔化,使閘極無法控制通道載子,造成通道載子直接在源汲之間導通。因此吾人可藉由判斷閘極是否能控制電晶體通道導通與否判斷儲存的狀態,因此可應用於OTP中。此種新型態與先前三種類別的OTP的操作機制完全不同,從而能夠繞過各大半導體廠設下的重重OTP專利壁壘,再加上本團隊已將dFuse的機制、操作方式與電路布局完整地在世界主要各國申請了專利,因此在IP保護上非常完整。另一方面,dFuse OTP不需要額外的光罩與特殊製程,只需利用foundry提供的CMOS製程即可下線並製作晶片,本團隊已在台灣前兩名foundries試量產成功。更重要的是,此OTP只需要兩顆電晶體串聯即可形成一記憶體胞,因此所需面積非常小,在成本上極具競爭力,非常適合應用對成本較為敏感的穿戴式行動裝置與元件中。 |

||

| 科學突破性 | dFuse OTP之技術突破:1.編程電壓<4V; 2.編程速度 20奈秒; 3. 讀取速度<10奈秒; 3.記憶窗口>十萬倍; 4.編程電壓與溫度無關; 5.在150度C使用>10年; 6.通過封裝reflow測試; 7.試量產40/28nm OTP晶片成功; 8. 記憶胞大小<0.06平方微米. |

||

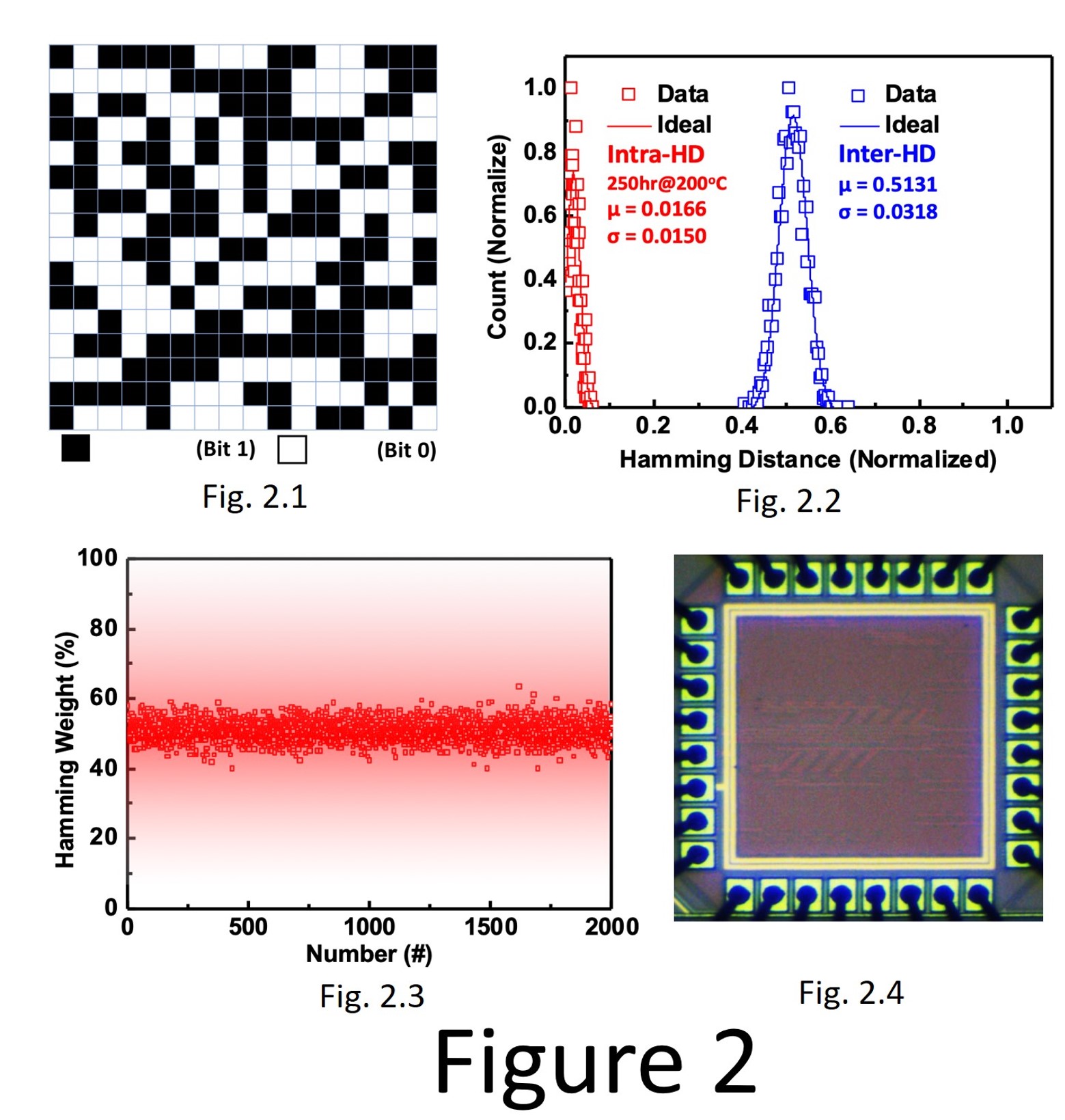

| 產業應用性 | dFuse-OTP PUFs產業應用性:1.5G-AIOT潛藏巨大資安危機;2.資安已列國家支持產業;3.PUF是資安產業核心硬體關鍵部位;4.OTP-PUF是市場上效能最好且成本最低; 4.40nm dFuse-OTP PUF的馬賽克圖,intra-HD,inter-HD,HW特性均超出業界標準. |

||

| 關鍵字 | 單次編程記憶體 嵌入式記憶體 非揮發記憶體 物聯網 人工智慧 資安 物理不可複製函數 晶片指紋 第五代通訊協定 介電質熔絲崩潰 | ||

| 備註 | 本研究團隊在CMOS平台上首度發現了閘介電層獨特的新型崩潰機制 (dielectric fuse breakdown- dFuse),並將此機制完整地發表於2015年IEDM會議上[4]獲得與會聽眾極大迴響,在這個基礎上,本團隊更進一步地利用28nm HKMG CMOS設計平台成功設計了「介電質熔絲型崩潰OTP記憶體電路晶片」達到低成本高密度之設計準則,並在2019年的Symposia on VLSI Circuit 會議上發表[5],更難能可貴的是本次作品受邀參加競賽海報欄目,與來自世界各地產學術界的頂極晶片設計專家好手同台競技,是該年度唯一一支來自台灣學術界的半導體研究團隊,引起世界關注,替台灣博得一次亮眼的出場機會。 進一步地,本團隊更向應用端整合開發,發表了基於dFuse崩潰機制的實體不可複製函數(OTP PUF),並成功驗證了此PUF在由5G驅動的物聯網(IoT)時代衍生的資安議題中抵禦駭客攻擊的能力[6]。相信不久地將來,很有機會可以在市場上看到相關產品出現。總而言之,本團隊是台灣固態學門領域中唯一一位具有將元件機制、晶片設計和市場應用結合起來的垂直整合經驗的年輕研究團隊。 |

||

- 聯絡人

- 謝易叡

- 電子信箱

- erayhiseh@ncu.edu.tw

其他人也看了