| 技術名稱 | 近場測試技術系統於電源整合與訊號整合分析應用 | ||

|---|---|---|---|

| 計畫單位 | 國立高雄大學 | ||

| 計畫主持人 | 吳松茂 | ||

| 技術簡介 | 半導體IC積體電路單晶片裸晶微小化,電子元件密集度以驚人速度增長,封裝測試產業More than Moore先進構裝技術發展趨勢,多晶片三維訊號互連之構裝與測試技術進展,封裝測試產業發展,從以往的單晶片訊號互連邁入多晶片三維訊號互連之技術,以增加單位面積下所能使用的電路佈線密集度,且對阻抗之控制以及高頻高速帶來之電磁干擾抑制能有其益處,如:多晶片系統化構裝(SiP)、三維多晶片堆疊構裝(3DIC)及扇出晶圓尺寸封裝(Fan-out PKG)等,讓人對於未來之產品在高功能集積前提下之微小化及高度功能密集化發展帶來無限的憧憬。當多項系統高度整合於系統模組時,系統功能高度集積於系統單晶片與系統封裝中,功能區塊間之訊號串擾(XTK)、輻射干擾與相容(EMI/EMC)、靜電損壞(ESD)及系統整合分析(PI/SI)驗證,成為系統廠商在個功能晶片設計及系統電路設計時重要的考量因素。 |

||

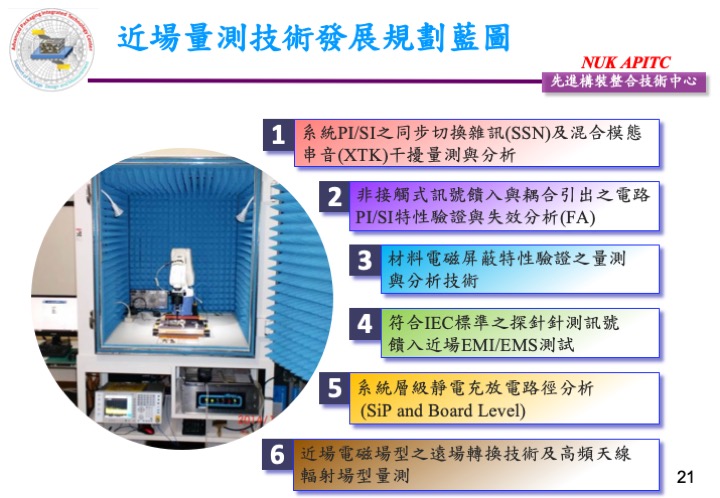

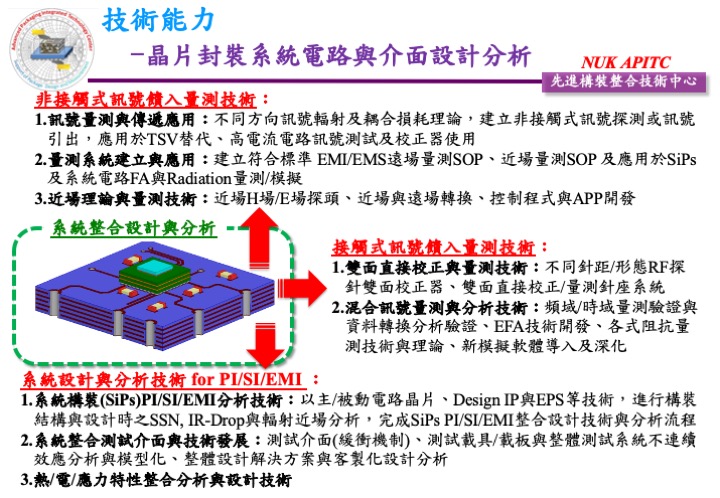

| 科學突破性 | 整合寬頻阻抗匹配雙面點針系統於近場系統中,導入時域/頻域訊號源及接收顯示系統,建立與開發具動態顯示系統電路靜電消散狀態之「系統電路靜電消散路徑檢測技術」、可顯示系統電路電源供應系統面共振模態之「同步切換雜訊檢測技術」及利用訊號干擾非接觸式耦合方式進行之「系統電路PI/SI最佳化設計」,技術領先業界。 |

||

| 產業應用性 | 研究發展對未來發展與產業應用帶來了廣大效益: |

||

| 關鍵字 | 雙面直接校正針測技術 近場量測 同步切換雜訊 電磁輻射 靜電消散路徑 時頻量測 訊號整合分析 電源整合分析 系統電路最佳化特性量測 電磁屏蔽材料分析 | ||

- 聯絡人

- 吳松茂

- 電子信箱

- sungmao@nuk.edu.tw

其他人也看了