| Technical Name | High-Speed Circuit Designs | ||

|---|---|---|---|

| Project Operator | National Taiwan University | ||

| Project Host | 李致毅 | ||

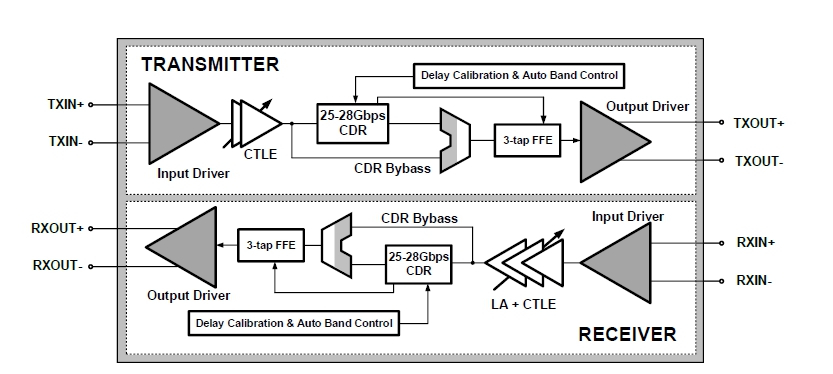

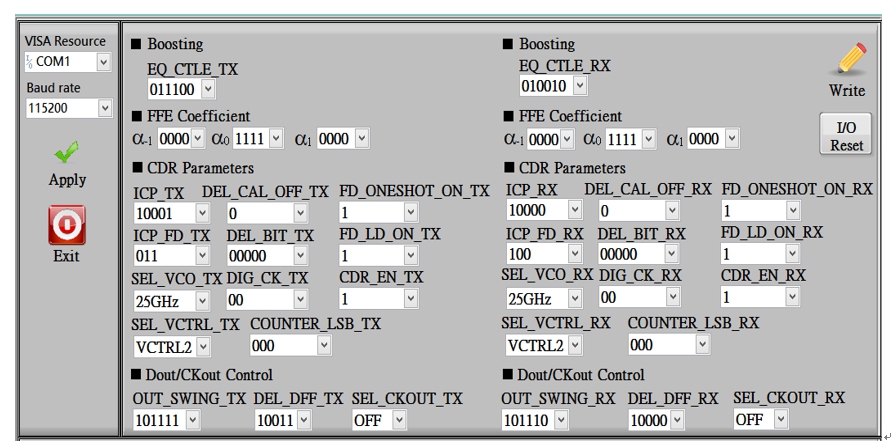

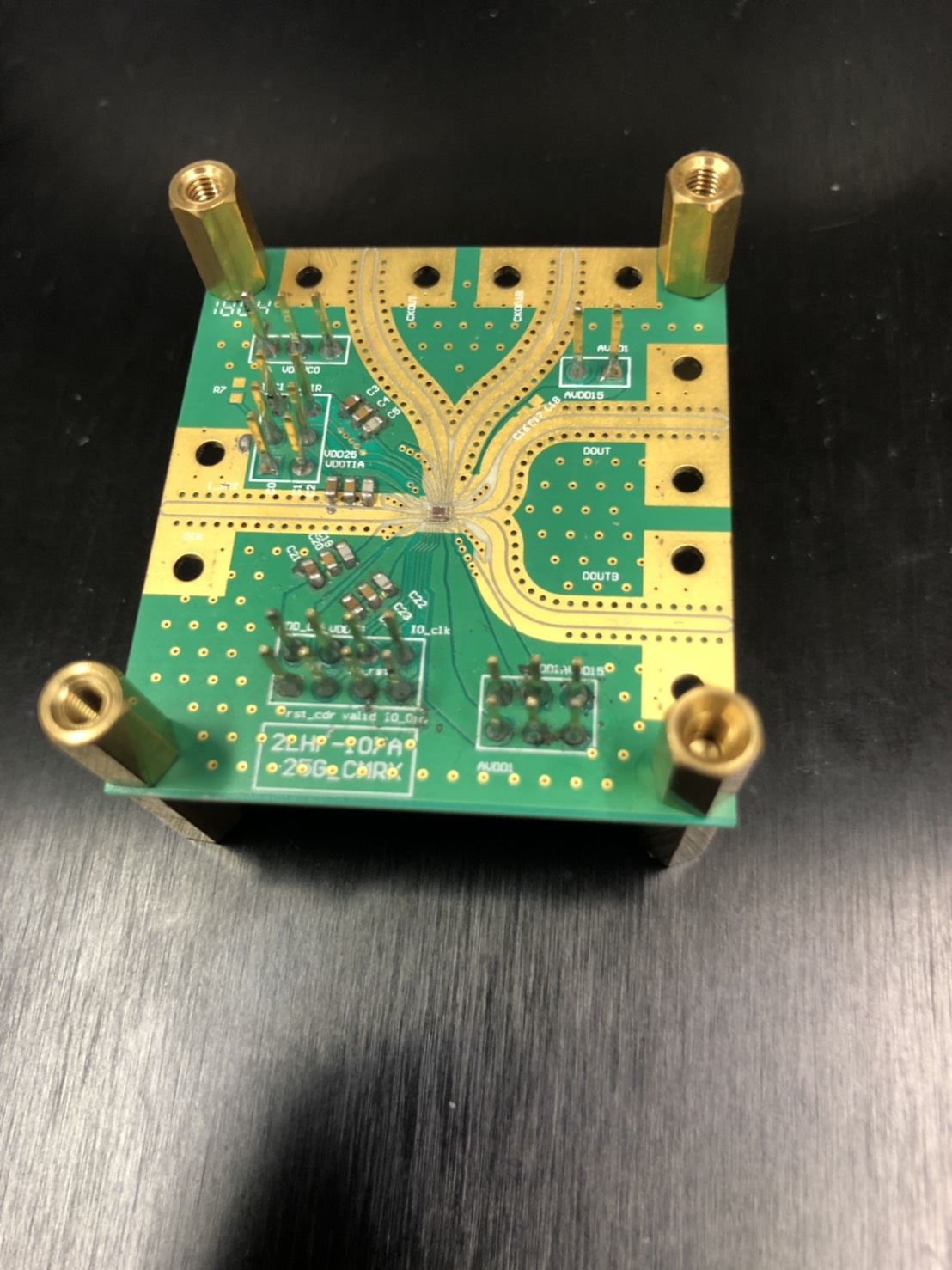

| Summary | The team has a forward-looking high-speed transmission communication chip development technology, respectively, to develop high-speed pulse pattern generator (PPG), high-speed data clock recovery circuit (CDR) and support burst mode (Burst mode), and use forward-looking advanced process to achieve High-speed, low-power, high-stability SerDes system chips. |

||

| Scientific Breakthrough | In recent years, NRZ or PAM-4 have been proposed. In order to achieve the forward-looking specifications of this project, the data type can be transmitted in the form of PAM-4 in the past. The effect, the loss on the power, the complexity of the circuit, the architecture of the equalizer, and the swing of the output stage are all factors to consider. |

||

| Industrial Applicability | The main reason is to operate the circuit design at high frequencies. The development of forward-looking projects must be expected to adopt novel circuit techniques to overcome the limitations of bandwidth and achieve low power. Low noise requirements. |

||

| Keyword | SerDes Pulse pattern generator Clock and Data Recovery Burst mode Decision Feedback Equalizer NRZ PAM-4 Equalizer Phase-locked loops Pseudo-Random Binary Sequence Generator | ||

- R07943170@ntu.edu.tw

other people also saw