| 技術名稱 | 高遷移率材料、製程、多層疊元件及熱電路模型;鐵電鉿基氧化物之負電容特性研究及相關應用;先進原子層材料與模組技術 | ||

|---|---|---|---|

| 計畫單位 | 國立臺灣大學台積電-臺灣大學聯合研發中心 | ||

| 計畫主持人 | 劉致為 | ||

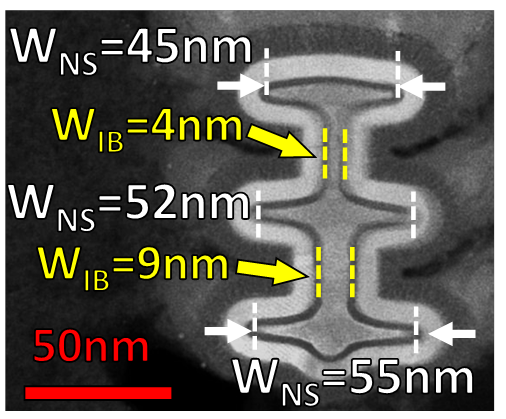

| 技術簡介 | 本計畫著重開發滿足智慧終端需求之下世代技術節點的材料、製程、元件及電路熱模擬之關鍵技術,製作具備鍺通道之多層疊環繞式電晶體並開發模組技術、三維負電容元件及相關模組技術、開發適用於類神經網路運算之鐵電材質憶阻器及進行嵌入式記憶體與元件之共模擬、低磊晶缺陷之鍺於矽基板上、研究磊晶成長速率。 |

||

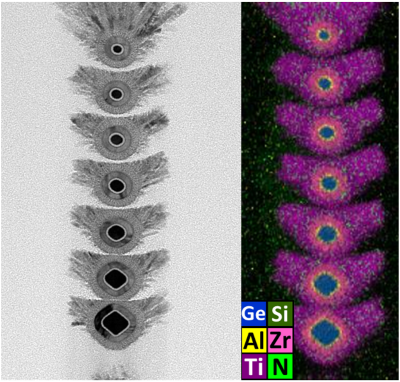

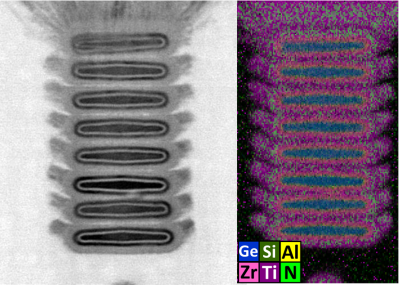

| 科學突破性 | 本計畫成功製備了世界首顆高效能七層堆疊鍺矽奈米線,與國際標竿相比,其驅動電流為鍺/鍺矽三維電晶體之世界紀錄。八層堆疊鍺矽奈米片之堆疊層數更超過法國半導體研究機構CEA-Leti發表於2020 年VLSI 的七層堆疊矽奈米片。 |

||

| 產業應用性 | 本計畫團隊將高層數堆疊高遷移率通道之研究成果,對比台積電的2 奈米技術節點(三層通道)與 Intel的20A技術節點(四層通道),八層/七層通道則可用於1.4奈米(14A)技術節點。團隊持續致力於更高層數通道堆疊之GAAFET,追求更高的電晶體驅動電流,提供半導體晶片更好的效能,持續推進技術節點。 |

||

| 關鍵字 | 鍺 磊晶 源汲極再成長 多層疊環繞式電晶體 負電容元件 原子層模組技術 微影技術 憶阻器 自發熱效應 功耗、性能、佔位面積與成本 | ||

- 聯絡人

- 劉致為

- 電子信箱

- cliu@ntu.edu.tw

其他人也看了