| Technical Name | 邊緣人工智慧推論系統之智產元件產生器 | ||

|---|---|---|---|

| Project Operator | National Chung Hsing University | ||

| Project Host | 賴永康 | ||

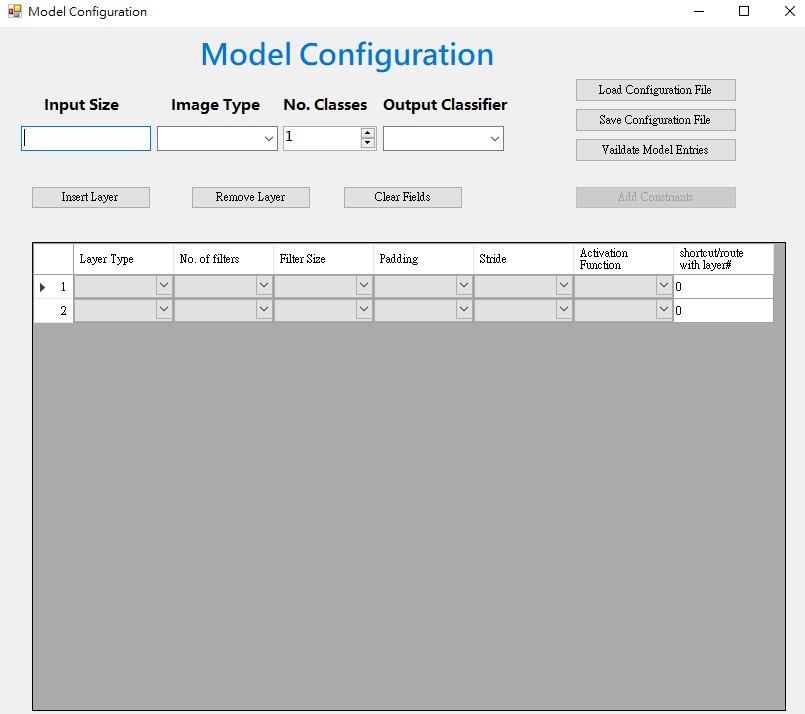

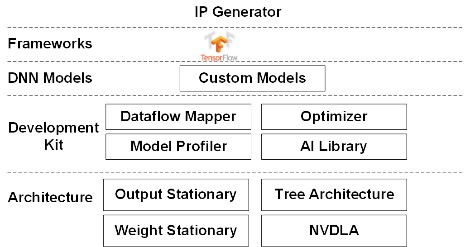

| Summary | "1. Automatically generate Verilog code tools based on the hardware architecture of convolutional neural networks: 4 different hardware architectures (output stationary, weight stationary, Tree architecture, NVDLA) can be generated for the currently more commonly used DNN networks. 2. Visual performance index analysis tool: According to the selected DNN model,the choice of hardware architecture specifications, analyze the performance index." |

||

| Scientific Breakthrough | "1. Automatically generate Verilog code tool based on the hardware architecture of convolutional neural network: Add the supported layer type: layer type: shortcut, route, upsample, depthwise convolution. 2. Visual performance index analysis tool: It can effectively analyze the performance of the model on the hardware architecture,select the appropriate hardware specifications to achieve the hardware acceleration of the DNN model." |

||

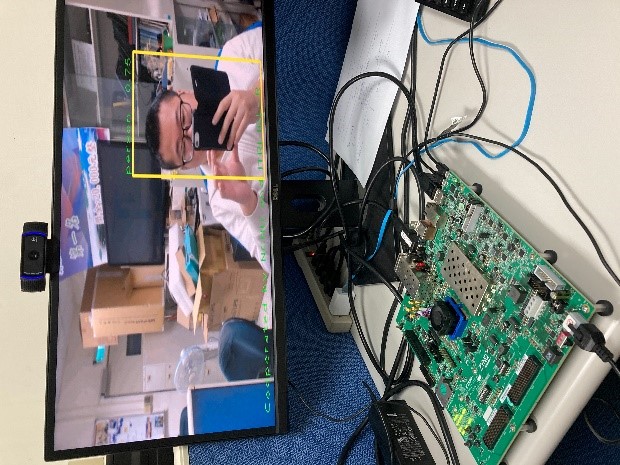

| Industrial Applicability | "Nowadays, many DNN models are used in various applications,many of them require hardware acceleration. To design the hardware accelerator architecture, different algorithmarchitecture options should be considered. For this reason, we design a general-purpose automatic generation of DNN hardware accelerator for the current popular DNN. We also design the Profiler to save the time of testing performance. We have a function for quick analysis of various performance indicators, so that users can select the most suitable hardware architecture for the model in the shortest time." |

||

| Matching Needs | 天使投資人、策略合作夥伴 |

||

| Keyword | Deep learning Neural Networks Hardware Architecture Mapping Automatic Verilog generator Profiler Systolic Array Tree Architecture NVDLA Object Recognition Optimization | ||

- shuchi@dragon.nchu.edu.tw

other people also saw